ISSN 2278 - 0211 (Online)

# A Novel Low Power Pulsed Latch with Increased Reliability

# Helen Judy. J.

P.G. Scholar, P.P.G. Institute of Technology, Coimbatore, Tamil Nadu, India **Kavitha D.**

Assistant Professor, P.P.G. Institute of Technology, Coimbatore, Tamil Nadu, India

#### Abstract:

The maturation in fabrication technologies of semiconductor integrated circuits results in rapidly shrinking technology node and aggressive scaling of voltage causes an increase in the probability of soft errors in advanced CMOS digital logic circuits. Many attempts to mitigate the soft errors ensue in significant cost penalties in terms of area, power and performance. The proposed method intents a pulsed latch with increased immunity, reliability and reduced power consumption for this purpose, a new transition detector is designed in order to detect single event transition. It shows a remarkable melioration in terms of power, area and performance when compared to conventional transition detector post layout simulation using CMOS 45nm. This detector is further engrafted into the latch to be used as register. The reliability and effectual functioning of proposed pulsed latch is compared with conventional register. The proposed system is designed using MICROWIND 3.1 to get efficacious output.

**Keyword:** Reliability, reduced power consumption, pulsed latch, transition detector

#### 1. Introduction

Reliability being the major design challenges for the CMOS technology in sub-micron are been impacted greatly by shrinking geometries, lower supply voltages, higher clock frequencies and higher densities [1]

Development of technology causes increase in the density of chip and more over to save power the operating voltage has become lower and lower. All these changes bring a comfortable portable device for us. But as these dimensions and operating voltages of electronic devices are reduced to satisfy the demands of higher density and lower power, circuit becomes more sensitive to externally induced phenomena such as cosmic rays and other high energy particles. One factor of reliability is sensitivity to these external induced particles which makes the circuit more susceptible to spurious voltage variation altering the node voltage values. These are extremely bad for flip flops and latches whose output depends on input data. This affects the integrity resulting in transient fault or single event transition, when latched by a sampling element results in soft error. This soft error occurs when ever the minimum charge deposited in the sensitive node of the flip flop to change the stored bit is less compared to the externally induced cosmic or high energy particles, and is also classified as single event upset in space communication [2-4].

A single event transient (SET) is a transient voltage pulse created due to a single event at a node in an integrated circuit. Under certain conditions, this transient pulse can propagate through the integrated circuit and eventually appear at the circuit's output. It may also be captured if it appears at the input of the latch during the setup and hold time of the latch (also known as (window of vulnerability). A SET, thus captured, becomes a single event upset. A single event upset (SEU) is a change of state caused by ions or electro-magnetic radiation striking a sensitive node in a micro-electronic device, such as in a microprocessor, semiconductor memory, or power transistors. The state change is a result of the free charge created by ionization in or close to an important node of a logic element (e.g. memory "bit"). The error in device output or operation caused as a result of the strike is called an SEU or a soft error. The SEU itself is not considered permanently damaging to the transistors or circuits' functionality unlike the case of single event latch up (SEL), single event gate rupture (SEGR), or single event burnout (SEB). These are all examples of a general class of radiation effects in electronic devices called single event effects.

An SEU can also be generated within a latch when a radiation event causes enough charge to be collected at a sensitive node in the latch. The minimum charge required to flip the state of the latch is termed as critical charge (Qcrit). Qcrit is a property of the particular circuit and depends on factors such as individual transistor currents and nodal capacitances. There are various soft-error mitigation techniques that can be implemented at the device, circuit and architecture levels. For instance, triple-well and silicon-on-insulator technologies are effective mitigation strategies at the device level, Triple Modular Redundancy (TMR) are mitigation techniques at the circuit-level whereas error correcting codes (ECC) and redundant execution are some of the soft-error mitigation schemes at the architecture-level. [6]

### 2. Previous Work

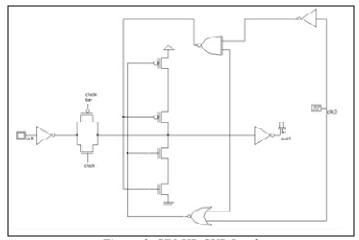

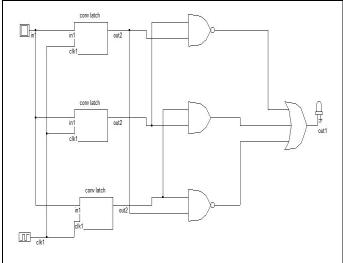

Many works have been reported to increase immunity of the registers. Some approaches increase the minimum amount of charge stored in sensitive node for changing the state of latch. For example, SIN-HR register, in which the number of sensitive nodes is reduced using two feedback paths and its modified version called "SIN-HR sub"[10] as in Figure 1 was designed for subthreshold region. Triple Modular Redundancy (TMR) [8] latch in Figure 2 achieves full immunity. However, it consumes more power, occupies more area and also imposes more delay penalty

The proposed structure improves reliability with lower performance compared to conventional registers. Transition detector designed to satisfy fast reaction that is necessary to mask single event effect.

Figure 1: SIN-HR-SUB Latch

Figure 2: TMR Latch

# 3. Transition Detector

Transition detector (TD) has always been ascertained as an undistinguished part and has just been implemented using a common model. The main source of difficulty of these circuits is their poor speed. They have also been designed for super threshold operation. Likewise data loss might also occur very often due to vast effects of process and environment variations and leakage in sub-threshold region.

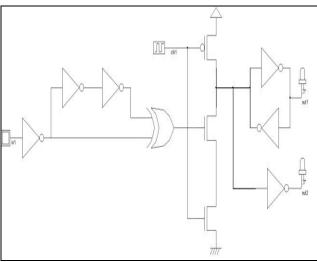

The Figure 3 (a) shows a conventional TD which is called as XOR-TD. It is not complex but fundament of all transition detectors. The pulse generated by XOR-TD can change the value of dynamic circuit. The weak loop which forms a keeper when added to dynamic node decreases the sensitivity to leakage, the dynamic node value becomes hard to change with this scheme. Further, adding delay causes wider pulses or might require a stronger NMOS which would result in more leakage and ensue in utilization of stronger loop or wider PMOS to prevent failure.

Figure 3: XOR-TD

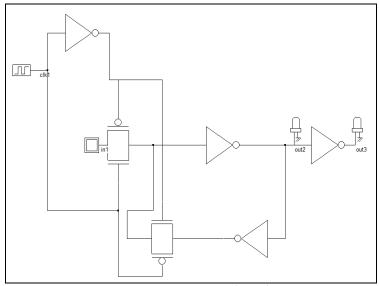

Figure 4: Proposed TD

Figure 5: Power consumption of Proposed Transition Detector

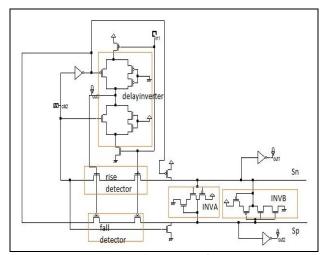

As shown in Figure 4, the proposed transition detector which has a differential outputs determines transition to high and low rapidly. The circuit consists of delay-inverter to delay input rise and fall detector to detect transitions, a PMOS and NMOS is employed for recovery and two inverters to keep output values against leakage and to set up propagation between differential outputs.

In delay- inverter, the transistors connected to the clock and clock-bar decreases the delay of input during transparent phase and achieves necessary delay during opaque phase, when these two transistors are off the signal flows through other transistors connected to them.

If D is high the rise detector circuit becomes active causing the output node Sn connected to it to be ground. This output node which is ground causes other output node Sp of the differential output to go high through Inverter A (INVA). If D falls the node Sp is changed to high through the fall detector circuit and the complemented values of node Sp propagates to node Sn through Inverter B (INVB). The extra transistors inserted to INVA and INVB ensures leakage reduction and the feedback structure ensues in very fast change of Sn and Sp.

The Comparison table shows the average power consumption of the proposed and the conventional transition detector, finally the proposed transition detector also has a smaller area. Hence provides a significant improvement in terms of delay, energy and area.

|                        | XOR  | Proposed |

|------------------------|------|----------|

| Power consumption (µw) | .621 | .104     |

| Delay (ns)             | 1.20 | 0        |

| Number of transistors  | 25   | 21       |

Table 1: Comparison of Transition Detector

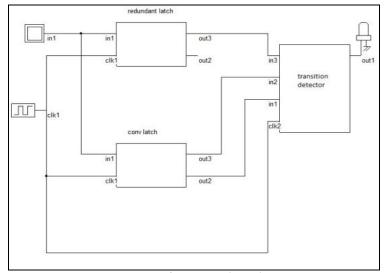

## 4. Reliable Pulsed-Latch

The purported transition detector is engrafted into a conventional latch presenting a new reliable latch. The TD switches the multiplexer designed using pass transistor on detecting a fierce transition. As TD acts promptly, output of the latch never notices soft error. In case an error occurs in the redundant latch, output never observes it as the output is connected to main latch. Besides the change in TD's value unobserved in output as it switches between two latches maintaining the correct values.

Figure 6: Proposed Latch

Figure 7: Conventional Latch

Figure 8: Power Consumption of Proposed Latch

The comparison table shows the average power consumption of the proposed reliable latch, SIN-HR-SUB and TMR. The proposed latch shows least power consumption than the previously existing latches.

|            | D-Q Delay(ns) | Power Consumption (mw) |

|------------|---------------|------------------------|

| SIN-HR-SUB | 1.20          | 0.130                  |

| TMR        | 0.40          | 0.362                  |

| Proposed   | 0.35          | 2.604µw                |

Table 2: Comparison of Power Consumption of Proposed Latch

The critical charge for each latch is calculated using (1) so as to model the soft error.

$$I(t) = (Q0/(T_t - T_f)) * (e^{-t/T_f} - e^{-t/T_f})$$

$$\tag{1}$$

Where  $Q_0$  is the collected charge,  $T_t$  is the time constant of collection and  $T_f$  is ion track establishment time constant. The time constant  $T_t$  and  $T_f$  are considered to be 165ns and 50ns respectively. Each node is assigned different values of  $Q_0$  to find the critical charge. This process sequentially is repeated for all nodes of each latch

The following table shows the comparison of robustness of the proposed latch. This shows that the proposed latch comes with increased reliability and better performance.

|            | Critical Charge               |

|------------|-------------------------------|

| SIN-HR-SUB | 1.3 (all nodes are Sensitive) |

| TMR        | 0 (Completely Robust )        |

| Proposed   | 0 (Completely Robust )        |

Table 3: Comparison of Robustness of Proposed Latch

#### 5. Conclusion

The proposed design shows increased reliability and better performance on comparing with the previous work in 45nm CMOS technology. The proposed transition detector enhances area occupation, performance and power significantly and the pulsed latch shows inherent immunity to single event transition and least power consumption compared to previous latches.

## 6. Refrences

- 1. M. Alioto, "Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 59, pp. 3-29, 2012.

- 2. K. A. Bowman, J. W. Tschanz, N. S. Kim, J. C. Lee, C. B. Wilkerson, S. L. L. Lu, et al., "Energy-efficient and metastability-immune resilient circuits for dynamic variation tolerance," IEEE Journal of Solid-State Circuits, vol. 44, pp. 49-63, 2009.

- 3. S. Buchner, M. Baze, D. Brown, D. McMorrow, and J. Melinger, "Comparison of error rates in combinational and sequential logic," IEEE Transactions on Nuclear Science, vol. 44, pp. 2209-2216, 1997.

- 4. S. Das, C. Tokunaga, S. Pant, W. H. Ma, S. Kalaiselvan, K. Lai, et al., "RazorII: In situ error detection and correction for PVT and ser tolerance," IEEE Journal of Solid-State Circuits, vol. 44, pp. 32-48, 2009.

- 5. V. K. Madisetti and D. B. Williams, The Digital Signal Processing: Handbook: C R C Press LLC, 1999.

- 6. G. C. Messenger, "Collection of Charge on Junction Nodes from Ion Tracks," IEEE Transactions on Nuclear Science, vol. 29, pp. 2024-2031, 1982.

- 7. M. Omana, D. Rossi, and C. Metra, "Latch Susceptibility to Transient Faults and New Hardening Approach," IEEE Transactions on Computers, vol. 56, pp. 1255-1268, 2007.

- 8. W. J. prove Van Gils, "A Triple Modular Redundancy Technique Providing Multiple-Bit Error Protection Without Using Extra Redundancy," IEEE Transactions on Computers, vol. C-35, pp. 623631, 1986.

- 9. P. N. Whatmough, S. Das, and D. M. Bull, "A low-power 1GHz razor FIR accelerator with time-borrow tracking pipeline and approximate error correction in 65nm CMOS," IEEE International in Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp. 428-429, 2013.

- 10. C. Yongsuk, K. Yong-Bin, and F. Lombardi, "Soft error masking latch for sub-threshold voltage operation," in IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 25-28, 2012.