ISSN: 2278 - 0211 (Online)

# Implementation Of Ultra Low Power High Speed 4-2 Compressor Using Single Phase Adiabatic Dynamic Logic

## D.Pradeep Kumar

M.Tech (VLSI&ES)

Parkasm Engg.college,

Kandhukur, Ongole, A.P, INDIA.

## R.Giri Prasad

Assoc. Professor, Dept. of E.C.E, Parkasm Engg.college, Kandhukur, Ongole, A.P, INDIA

Abstract: The paper presents the implementation of ultra low power 4-2 Compressor circuit operated by single-phase adiabatic Dynamic logic (SPADL) which, unlike any other existing Adiabatic logic family uses single sinusoidal supply-clock. This not only ensures high energy efficiency, but also simplifies the clock design which would be otherwise more complicated due to the signal synchronization requirement. Static logic resembled characteristics of SPADL logic substantially decreases circuit complexity with improved driving ability and circuit robustness. In TSMC 0.18µm CMOS technology. CADENCE simulations show that SPADL saves 65% to 50% and 30% to 40% of total energy compared to Conventional CMOS and other existing single phase adiabatic logic based 4-2 Compressor for a frequency of 1MHz to 100MHz.

**Keywords:** Single-phase, Adiabatic Logic, Energy efficiency, High speed, 4-2 Compressor

#### Introduction

As the semiconductor process has stepped into the deep submicron phase, the transistor counts integrated in a single chip are increasing continuously. Significant reduction of on chip power density, therefore, has received considerable favour. The dynamic switching is accounted the ring leader of the total power dissipation. As a response, over the past decade, though many techniques have been developed to reduce such an unwanted power overhead, yet adiabatic logic becomes the promising alternative. Adiabatic circuits achieve low energy dissipation by restricting the current flow across devices with low voltage drop and by recycling the energy stored on their load capacitance by using a time varying AC supply voltage. Recent years have seen various Energy Recovery Circuits (ERCs) toward adiabatic circuitry for ultra-low power implementation. Most of them require a four-phase or two phase power-clock. Typical examples are four-phase CPAL [1] and two-phase 2N2N2P2D [2], CEPAL [3], GFCAL [4]. In multiphase clocking scheme, implementation of complex control schemes [5]-[7] distribution of multiple clock phases[3]-[7], the management of data dependent clock capacitance fluctuations make the multiphase clocking schemes sensitive to clock skew and may severely limit their high frequency performance [8]-[9]. In contrast to multiphase circuits, single phase adiabatic circuit relies on just one phase of a power clock waveform for low power and synchronization. Simply a sinusoidal signal can be used as a power clock in a single phase adiabatic circuit. This sinusoidal waveform can be generated with higher energy efficiency than trapezoidal waveforms. In order to make adiabatic logic circuits more feasible and practical in VLSI CMOS applications, single phase operation of the circuits would be needed.

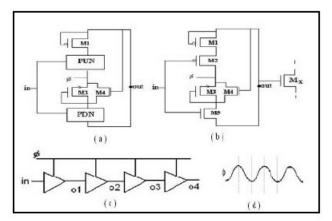

Figure 1: (a) SPADL general block (b) SPADL Inverter (c) SPADL inverter chain (d) Single phase supply clock

Previously reported SCALD [11] and SCAL [12] circuits use a single-phase powerclock, but the additional reference voltage and current increase the design complexity. Moreover these logic styles are difficult to design due to the optimal value of reference voltage concerning about clock frequency [11], [12]. An inverter chain using CAL logic is discussed in [13] with additional timing control clocks to ensure correct operation, resulting in complicated clock tree design and more energy dissipation. Moreover as CAL logic is based on differential signalling, it's higher switching activity reduces energy efficiency. Another typical single-phase ERC family is PAL [16], which is not considered as a real single-phase based ERC since its cascaded circuits need two complementary sinusoidal power clocks. Also PAL [16] logic gates suffer from undesired capacitive couplings, since the output nodes are kept floating instead of zero. Though QAPG [14] has reported as single phase adiabatic logic, yet transistor overheads decrease the energy efficiency. Motivated by the advantages of single phase adiabatic logic the authors have proposed a quasi-static single phase adiabatic dynamic logic (SPADL) [10] recently and also implemented the sequential subsystem. In this paper an 8 bit CLA has implemented by using SPADL logic all the simulations are done by Cadence Spice spectra in TSMC 0.18um technology and CMOS n-well process and results are compared with some imperative adiabatic logic styles (CAL, QAPG and 2N2N2P2D) including static CMOS also.

#### Overview Of Spadl Logic

SPADL requires only one sinusoidal power clock supply, Has simple implementation, and performs better than the Previously proposed diode based logic families [2]-[4] in terms of energy consumption. SPADL logic features Simplicity and static logic resembled characteristics, which Substantially decreases transistor overheads and the circuit Complexity.

## Configuration and Operation

Fig. 1(a) and (b) shows the general configuration of SPADL logic block and SPADL inverter. In Fig. 1, on basis of applied logic inputs, either pull up or pull down network (PUN or PDN) will be ON at any time instant. The charging and discharging operations of output (out) node of Fig. 1(a) can be described as follows:

a) When PUN is ON and 'out' is low, if supply clock (φ) ramps up 'out' node will be charged through PUN→M1 by following φ closely and higher logic will be obtained at out node. When  $\varphi$  ramps down, charges will be stored at 'out' node, as **they cannot flow** back to the supply clock  $(\varphi)$  due to reverse biased M1.

- b) When PDN is ON and 'out' is high, if φ ramps down, Charge stored at 'out' node flows back to the supply clock (φ) through the PDN→M3and M4.

- c) When PUN is ON and 'out' is high, if φ ramps up 'out' node will not transit for that clock period. So voltage level of 'out' node will not vary.

- d) When PDN is ON and 'out' is low, 'out' node voltage will not transit for that complete clock cycle. Hence

$$V(1) = (\varphi|_{\text{max}} - |V_{\text{TP}}|)$$

$$V(0) = \Delta V \tag{1}$$

Where  $\Delta V$  is proportional to f (Rd). Rd is the discharging path resistance. As discharging path consists of parallel combination of M3 and M4, Rd will be very low, which improves the lower swing.

Also due to finite voltage drop across M5, gate to source voltage swing of M4 increases. ON resistance ( $R_d$ ) of a NMOS can be expressed as

$$Rd \propto (VGS-VT)^{-1}$$

(2)

So increased gate to source swing reduces the ON

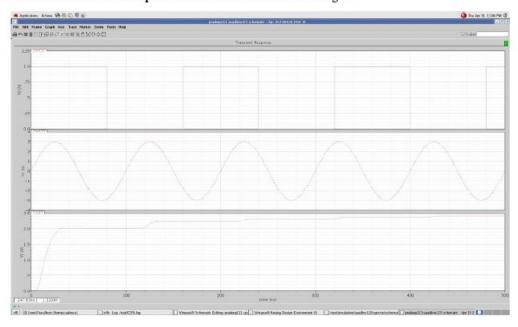

Resistance of M4. The output wave forms are shown in Fig. 2.

Figure: 2 Output waveform of SPADL inverter

Fig. 3 illustrates the operation of the SPADL inverter circuit. Assuming the applied inputs of the circuit areall valid at t=0 time instant. The 1st stage produces its valid-1and valid-0 outputs at t=T/2 time and t=T, respectively. The2nd stage produces its valid-0 output at t=T. Similarly, valid-1outputs of the 2nd and 3rd stages are both produced at t=3T/2, while the valid-0 outputs of the 3rd and 4th stages are both produced at t=2T, and so on. Thus, the total time, Total, needed for data to pass through the 4-stage circuit is 5T/2, where T is the period of  $\Phi$ . In general, for an N-stage circuit, we have Total= (N+1)T/2. When N >>1, Total = NT/2, which ensures higher speed of SPADL logic. Also in SPADL by using low clock frequency we can drive high frequency input signal.

Figure: 3 Operation of SPADL inverter, V1 and V0 are valid '1' and valid '0' output

Energy Consumption of SPADL Logic Circuit

In this section, energy consumption of SPADL logic block, say inverter, are analysed. From Fig 1, on the basis of input logic level when the supply clock  $(\phi)$  ramps up (or down) energy dissipation occurs across PMOS diodes (or NMOS diodes) and PUN (or PDN). As PMOS diodes with PUN (or NMOS diodes with PDN n/w) provide the charging (or discharging) path, energy dissipation across diodes can be

Expressed as;

$$\begin{split} \mathbf{E}_{\text{Dieds}} &= \mathbf{J}_{0}^{\text{T1}} | \mathbf{V}_{\text{TP}} | \mathbf{i}(\mathbf{t}) d\mathbf{t} \\ &= \mathbf{J}_{0}^{C_{\text{L}}(\mathbf{V}_{\text{DD}} - |\mathbf{V}_{\text{TP}}|)} | \mathbf{V}_{\text{TP}} | d\mathbf{q} \\ &- \left[ \mathbf{C}_{\text{L}} | \mathbf{V}_{\text{TP}} | (\mathbf{V}_{\text{DD}} - |\mathbf{V}_{\text{TP}}|) \right] \end{split} \tag{3}$$

Where  $T_1$  is the time taken by the supply clock to raise From 0 to VDD,  $^{|V}TP|$  is threshold voltage of PMOS diodes,  $C_L$  (= CD1 + CW + CGX) is the output load capacitance. CGX (=  $\beta LC_{OX}$ ) is the gate capacitance of next stage NMOS  $M_X$ .  $\beta$  and L are aspect ratio and length of the channel of MX and COX is the gate oxide capacitance per unit area.  $C_W$  is the wiring capacitance. EDiode is independent of operating frequency of supply clock. As clock frequency goes higher, the "diode transistors" have to be sized up proportionately. Moreover threshold voltage drop across PUN and finite ON resistance produce the energy dissipation ( $E_{Tx}$ ) in charging event and can be shown by the following expression

$$ETx=[\frac{1}{2}CL|VTP|^{2}+(RPCL/T)CL(VDD-|VTP|)^{2}]$$

(4)

Therefore for each logic transition total energy dissipation (E Total) in charging path becomes:

E Total = E Diode + ETx

$$\approx [CL|VTP|(VDD-|VTP|)] + [\frac{1}{2}CL|VTP|^{2}]$$

(5)

During discharging almost same amount of energy dissipates in the discharging path. So the maximum possible energy saving of SPADL logic over CMOS in a full clock cycle is  $n\% = \{ [CL|VTP|(VDD-|VTP|)] + [\frac{1}{2}CL|VTP|^2] / CLVDD^2 \} x 100$

$$\approx 2\alpha \left[1 - \alpha^2/2\right] \times 100 \text{ where } \alpha = \{|V_{TP}|/V_{DD}\}\$$

(6)

It is seen that there is no significant improvement in energy efficiencies of SPADL logic by lowering threshold voltage of PMOS and NMOS diode. However to achieve higher integration density or to maintain high drive current, voltage scaling is important. Still we cannot reduce threshold or supply voltage arbitrarily. As aggressive scaling of technology results in different leakage components become a significant issue of total power dissipation in adiabatic CMOS logic circuit measures proportionately more than is customary. This measurement and others are deliberate, using specifications that anticipate your paper as one part of the entire proceedings, and not as an independent document. Please do not revise any of the current designations.

# 4-2 Compessor By Spadl Logic

In this section, we first describe SPADL gates, and then we Present the design of adiabatic gates and 4-2 compressor using SPADL logic

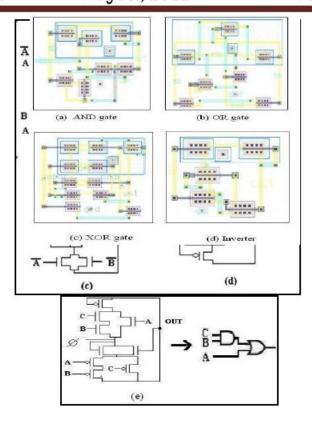

## SPADL Complex gate Design

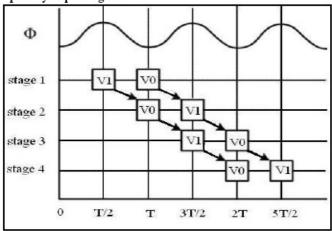

Complex gates can be easily implemented by using simple CMOS pull-up and pull-down network. In Fig. 1(a), by replacing the PUN (pull up network) or PDN (pull down network) we can implement the AND gate, XOR gate, 2 to 1 MUX with SPADL circuit topology. Fig. 4 shows implementation of all these gates with simple buffer circuit also. Static logic resembled characteristics of SPADL logic Substantially decreases the transistor overheads in complex gate design. In buffer circuit we have modified our logic slightly shown in Fig. 4 (d). When Φ ramps up and 'in'=1 (or 0), NMOS (or PMOS) (having gate i/p 'in') is turned ON and 'out' node is charged (or discharged). So we get same logic as 'in' at out node and hence the circuit acts as buffer. Thus Complex gate design can be made very modular and simple. The layouts of SPADL AND, OR, XOR and NOT gates are shown in Fig. 5. These layouts are created by using CADENCE suite based on TSMC 0.18µm CMOS n-well process technology. A design rule checking (DRC) and the circuit structure extraction are performed on the layout view of the adiabatic system. Then, the view extracted from the layout and the original schematic view is compared with the layout versus schematic (LVS) tool Layout of SPADL gates are shown in Fig. 5

Figure: 4 SPADL gates (a) XOR (b) 2 to 1 MUX (c) AND (d) buffer (e) AND\_OR having o/p (A+BC)

# SPADL 4-2 Compressor implementation

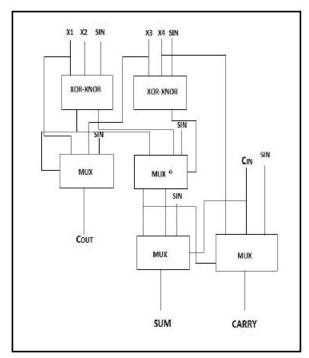

The 4-2 compressor has 4 inputs X1, X2, X3 and X4 and 2 outputs Sum and Carry along with a Carry-in (Cin) and a Carry-out (Cout) as shown in Fig 6. The input Cin is the output from the previous lower significant compressor. The Cout is the output to the compressor in the next significant stage. We can make XOR-XNOR simply connecting the inverter to the XOR gate output, also MUX\* can make connecting inverter to the MUX gate output.

Figure: 5 Layout of SPADL gates (a) AND (b) OR (c) XOR (d) Inverter (e) Mux

We can be observed that the overall delay is decreased the fact that both the output and its complement are available at every stage, is neglected thus replacing some XOR blocks with multiplexer's results in a significant improvement in delay. Also the MUX block at the SUM output gets the select bit before the inputs arrive and thus the transistors are already switched by the time they arrive. This minimizes the delay to a considerable extent. This is shown in Fig.6 A significant speed improvement in the implementation of 4-2 Compressor.

Figure: 6 Proposed 4-2 Compressor Architecture

The equations governing the outputs in the proposed architecture are shown below

Sum=

$$(x1 \oplus x2) \bullet x3 \oplus x4 + (x1 \oplus x2) \bullet (x3 \oplus x4) \bullet Cin+$$

$$(x1 \oplus x2) \bullet x3 \oplus x4 + (x1 \oplus x2) \bullet (x3 \oplus x4) \bullet Cin$$

$$Cout=(x1 \oplus x2) \bullet x3 + (x1 \oplus x2) \bullet x1$$

$$Carry=(x1 \oplus x2 \oplus x3 \oplus x4) \bullet Cin+(x1 \oplus x2 \oplus x3 \oplus x4) \bullet x4$$

The critical path delay of the proposed implementation is -XOR + 2\*-MUX.We have designed and simulated a 4-2 compressor using SPADL the simulations are done by

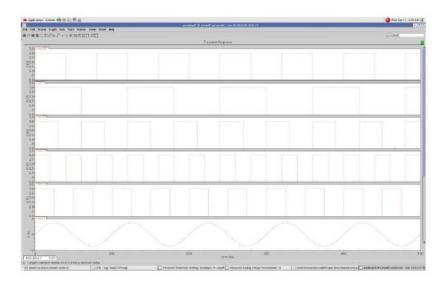

CADENCE spice spectra, using TSMC 0.18µm CMOS technology. A 5V peak-to peak sinusoidal voltage supply was used as the power clock F throughout our simulation for SPADL logic. The other adiabatic compressor blocks are simulated under different clocks provided by the literatures all the output nodes are loaded by25 fF or 5pf capacitors to get more stable waveform. The simulated waveforms are shown in Fig. 7.In order to fairly compare the energy efficiency of SPADL, CAL, QAPG, 2N2N2P2D and static CMOS, we have optimized the transistor sizes for each circuit style with the purpose of making them consume the least energy. Fig 8 show that the layout of the SPADL 4-2 compressor.

Figure: 7 Output waveforms of 4-2 adiabatic Compressor

## Simulation Results And Discussion

The results of the RTL compilation are shown bellow:

The results coming from the CADENCE simulation of the SPADL arithmetic units described above are presented and Discussed in this section and different aspects of SPADL logic has been explored due to the simulation. In this section energy dissipation measurements were determined directly from the CADENCE simulations outputs, by integrating the power over the period of oscillation. For the adiabatic circuits we have initially assumed a 100% energy- efficient power- clock generator, in order to compare the Results with the literature.

Figure: 8 Layout of SPADL 4-2 compressor

Figure: 9 IO PAD of SPADL 4-2 compressor

We take it into our account then SPADL shows better efficiency as it uses energy efficient sinusoidal source, compared to other multiphase clocked logic at low frequency, all single phase logic styles (CAL QAPG and SPADL) promise substantial energy savings compared to static CMOS, with the lowest energy consumption from SPADL. SPADL based compressor consumes only 34% and 52% of total energy consumed by conventional4-2 compressor at 10MHz and 100 MHz frequencies If respectively as diodes using MOS transistors are weak in driving capability, hence in SPADL based compressor, latches are introduced at the end of 3 stages to improve the driving ability That causes some extra power dissipation. Still at 100 MHz frequency, SPADL logic based compressor consumes only 62% and69% energy of the CAL and QAPG

Based 4-2 compressor respectively. In general energy consumption of SPADL logic does not depend on the

Figure: 10 RTL schematic of SPADL 4-2 compressor

Operating frequency so much at low frequencies as it is mainly due to the diodes and conventional clocks. As clock frequency goes higher, the "diode transistors" have to be sized up proportionately, which increases the capacitances. The resistive dissipation (which is proportional to RC/T) increases as well. On the other hand, 2N2N2P2D compressor does not show much power savings since 2N2N2P2D logic circuit has floating output node during part of the clock cycle. Simulation shows that this circuit can only work well if there is substantial capacitance to ground. Otherwise, capacitive coupling between the floating output node and clock would cause inadequate operating margins, which is undesirable as the output is directly connected to the input of the next stage logic in 2N2N2P2D. In QAPG compressor transistor overheads increase the power dissipation in path hence decrease the efficiency at high frequency regime. Though CAL

and QAPG logic based compressor promise substantial energy saving at low frequency yet in high frequency regime both circuit consume much more power compared to proposed SPADL compressor circuit. SPADL based compressor save almost 30% to 40% of total energy compared to CAL and QAPG at 100MHz frequency.

## Conclusion

This paper presents the SPADL 4-2 COMPRESSOR circuits using single phase ac power supply. This SPADL logic style can enjoy minimal control overheads and are thus capable of Operating at high speeds, while achieving high-energy efficiency. Compared to other existing single phase based Logic SPADL COMPRESSOR saves 30% to 40% of total energy for clock frequencies ranging from 1MHz to 100 MHz frequency. High energy efficiency of SPADL makes it suitable for implementing performance efficient VLSI circuitry.

#### Reference

- Jianping Hu, Tiefeng Xu, and Hong Li "A lower-power register complementary pass-transistor adiabatic logic IEICE Trans on Inf. & Sys., vol. E88-D, No. 7, 2005, pp.1479-1485

- Y. He, J. Tian, X. Tan and H. Min, "Quasi-static adiabatic logic 2N-2N2P2D Family" Electron. Lett., vol. 42, no. 16, 3rd August 2006.

- Cihun-Siyong Alex Gong, Muh-Tian Shiue, Ci-Tong Hong, and Kali-Wen Yao, "Analysis and Design of an Efficient Irreversible Energy Recovery Logic in 0.18μm CMOS," IEEE Trans. Circuits Syst. I, vol. 55, No. 9, pp. 2595-2607, Oct. 2008

- N.S.S. Reddy, M. Satyam, and K.L. Kishore, "Minimization of energy dissipation in glitch free and cascadable adiabatic logic circuits", TENCON 2008, p.p 1-5, Nov. 2008.

- 5. S. Nakata, Adiabatic charging reversible logic using a switched capacitor regenerator, IEICE Trans. Electron., vol. E87-C, no. 11, pp. 1837.1846, Nov. 2004

- J. Svensson, and J. G. Koller, Adiabatic charging without inductors, in Proc. IEEE Int. Workshop LowPower Design, IWLPD '94), Napa Valley, CA, April 22-27, 1994, pp. 159-164.

- D. Maksimovic and V.G. Oklobdziaja, "Integrated Power Clock Generator for Low-Energy Logic," in 21st Eur. Solid State Circuit Conf., Lillie, France, Sept. 1995.

- 8. J. M. Rabaey, A. Chandrakasan, and B. Nikolic, Digital Integrated Circuits: A Design Perspective (2nd edition). New York: Prentice Hall,.

- J Neil H. E. Weste, David Harris, and Ayan Banerjee, CMOS VLSI Design: A circuits and system perspective (3rd edition), Pearson education, 2008.

- M. Chanda, A. Dandapat, and H. Rahaman, "Ultra low power Sequential circuit implementation by a quasi static single phase Adiabatic dynamic logic," accepted in TENCON 2009, Singapore, Nov. 2009.

- S.Kim and M.C.Papaefthymiou. "Single-phase source-coupled adiabatic logic," in Proc. Int. Symp. Low-Power Electron. Design, San Diego, CA, Aug. 1999, pp. 97– 99.

- 12. Kim and M. C. Papaefthymiou, "True single-phase adiabatic circuitry," IEEE Trans. VLSI Syst., vol. 9, pp. 52--63, Feb. 2001.

- D. Maksimovic and V. G. Oklobdzija, "Clocked CMOS adiabatic logic with single ac power supply," in 21st Eur. Solid State Circuits Conf. Lille, France, Sept. 1995

- 14. E. K. Loo, H. I. A. Chen, J. B. Kuo, and M. Syrzycki., "Low-voltage single phase clocked quasi adiabatic pass gate logic," in CCECE 2007, Vancouver, April 200

- J. Svensson, and J. G. Koller, Adiabatic charging without inductors, in Proc. IEEE Int. Workshop LowPower Design, (IWLPD '94), Napa Valley, CA, April 22-27, 1994, pp. 159-164.

- Oklobdzija, V.G., Maksimovic, D., and Lin, F.C., 'Pass-transistor adiabatic logic using single power-clock supply," *IEEE Trans. Circuits Syst II, Analog Digit. Signal Process*, 1997, 44, (10), pp. 842–846.

- 17. Chanda, M.Adv. VLSI Design Centre, Meghnad Saha Inst. of Technol., Kolkata, India "implementation of ultra low power 8 bit cla using single phase adiabatic and dynamic logic" by Naha, S.; Manna, S.; Dandapat, A.; Brahman, H,December2010,pp.360-364

- 18. Centre for VLSI & Embedded Syst. Technol., Int. Inst. of Inf. Technol., Hyderabad "novel architectures for high spped and low power 3-2,4-2 and 5-2 compressors" by Kirthi M Krishna; Lingamneni Avinash; Sreekanth Reddy Puppala; M.B. Srinivas.