<u>ISSN:</u> <u>2278 – 0211 (Online)</u>

# Design and Synthesis of Sequential Circuit Using Reversible Logic

#### Mr. Sandesh.N.G

PG Student, VLSI Design and Embedded System, B.G.S. Institute of Technology, B.G.Nagar, Karnataka, India Mr. Manojkumar.S.B

Assistant Professor, Dept. of Electronics and Communication Engineering, B.G.S. Institute of Technology, B.G.Nagar, Karnataka, India

### Abstract:

The reversible logic will be having more importance in today's era due to its low power consumption. It will be having more applications in quantum computing and low power VLSI design. This paper proposes the different reversible sequential circuits. Proposed circuits are simulated using Xilinx ISim simulator and implemented on Xilinx FPGA platform.

Key words: Reversible Logic, Reversible Logic Gates, D-Latch, T-FlipFLop, Asynchronous Up/Down Counter.

### 1.Introduction

According to R. Landauer's research, the amount of energy dissipated for every irreversible bit operation is at least KTln2 joules, where K=1.3806505\*10<sup>-23</sup>m<sup>2</sup>kg<sup>-2</sup>K<sup>-1</sup> (joule/Kelvin<sup>-1</sup>) is the Boltzmann's constant and T is the temperature at which operation is performed [1]. In 1973, Bennett showed that KTln2 energy would not dissipate from a system as long as the system allows the reproduction of the inputs from observed outputs [2]. Reversible logic supports the process of running the system both forward and backward. This means that reversible computations can generate inputs from outputs and can stop and go back to any point in the computation history. A circuit is said to be reversible if the input vector can be uniquely recovered from the output vector and there is a one-to-one correspondence between its input and output assignments, i.e. not only the outputs can be uniquely determined from the inputs, but also the inputs can be recovered from the outputs Energy dissipation can be reduced or even eliminated if computation becomes Information-lossless.

## 2. Reversible Logic

A reversible logic gate will be having n-input n-output with one-to-one mapping. This helps to determine the outputs from the inputs and also the inputs can be uniquely retrieved from the outputs. In the synthesis of reversible circuits direct fan-Out is not. In reversible logic gates feedback paths are not allowed. However fan-out in reversible circuits is achieved using additional gates. Optimized or efficient reversible logic circuits will be minimum number of reversible gates, garbage outputs, constant inputs and minimum quantum cost. There are several basic reversible logic gates are available in the literature. In the below section we discuss some basic reversible logic gates that are used for our proposed work

## 3.Basic Reversible Logic Gates

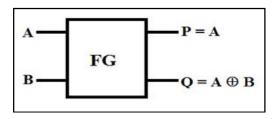

### 3.1.Feynman Gate (FG)

Feynman gate [3] is a 2\*2 reversible gate is shown in Figure 1. The input vector is I(A, B) and the output vector is O(P, Q). The outputs are defined by P=A, Q=A  $\square$  B. Quantum cost of a Feynman gate is l.

Figure 1: Feynman Gate (FG)

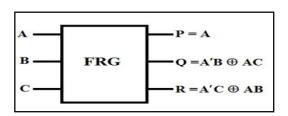

# 3.2.Fredkin Gate (FRG)

Fredkin Gate (FRG) [3] is a 3\*3 reversible gate is shown in Figure 2. The input vector is I (A, B, C) and the output vector is O(P, Q, R). The output is defined by P=A, Q=A'B $\Box$ AC and R=A'C $\Box$ AB. Quantum cost of a Fredkin gate is 5.

Figure 2: Fredkin Gate (FRG)

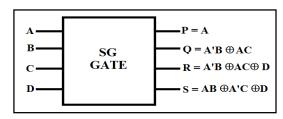

# 3.3.Sayem Gate (SG)

Sayem gate (SG) [4] is a 4x4 reversible gate is shown in Figure 3. The input vector is I (A, B, C, D) and the output vector is O(P, Q, R, S). The output vector is defined by P = A,  $Q = A'B \square AC$ ,  $R = A'B \square AC \square D$ ,  $S = AB \square A'C \square D$ . Quantum cost of a Sayem gate is 6.

Figure 3: Sayem Gate (SG)

# 4.Proposed Work

#### 4.1.D-Latch

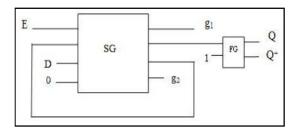

The D flip-flop [5] is a circuit that needs only a single input and clock pulses. The action of the D flip-flop is straightforward. The Figure 4 shows the proposed reversible D-Latch.

Figure 4: Proposed D-Latch

# 4.2.T-FlipFlop

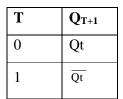

As the name suggests, T flip-flop [6] circuit used to toggle the output when input is high (1) and retains the output when input is low (0), thus it does two operation, it either holds the last state or toggles the output. Essentially, it has a logical symmetry with controlled NOT kind operation. Table I shows the truth table of T-FlipFlop. Figure 5 shows proposed reversible T-FlipFlop.

Table 1: Truth Table of T-FlipFlop

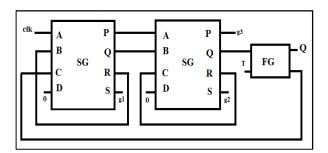

Figure 5: Proposed T-FlipFlop

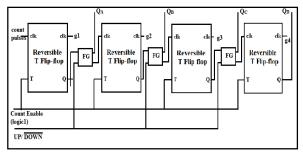

# 4.3. Asynchronous Up/Down Counter

The implementation of 4-bit reversible asynchronous Up/Down Counter is shown in Figure 6 [6]. The Up/Down operation of this reversible circuits is controlled by the control input UP/DOWN. For UP operation, the control input should be 1 and for down operation, the control input should be 0.

Figure 6: Proposed 4-Bit Asynchronous Up/Down Counter

### **5.Simulation Results**

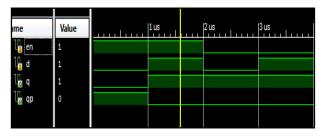

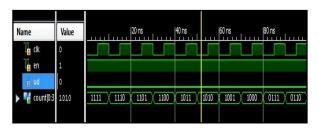

The entire architecture is modeled using VHSIC hardware description language (VHDL). The coding is done on Xilinx ISE13.2 on Spartan 3 using target device: XC3S50-PQ208 at speed grade of -5. For simulation purpose the Xilinx ISim simulator has been used. The simulation result for D-Latch is shown on Figure 7 for T-FlipFlop is shown on Figure 8 and for 4-Bit Asynchronous Down counter is shown on Figure 9.

Figure 7: Simulation result of proposed reversible D-Latch

Figure 8: Simulation result of proposed reversible T-Latch

Figure 9: Simulation result of proposed reversible 4-bit asynchronous down counter TABLE II, TABLE III and TABLE IV shows comparative experimental results of Different Reversible D-Latch, T-FlipFlop and 4-Bit Asynchronous Up/Down Counter.

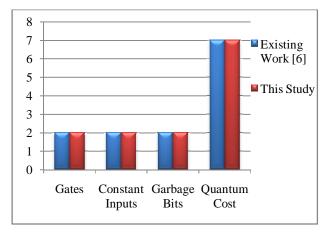

|                   | No. Of gates | No. of Constant Inputs | No. of Garbage Bits | Quantum Cost |

|-------------------|--------------|------------------------|---------------------|--------------|

| Existing Work [6] | 2            | 2                      | 2                   | 7            |

| This Study        | 2            | 2                      | 2                   | 7            |

Table 2: Comparative Experimental Results of Different Reversible D-Latch

Figure 10: Graphical representation of comparison of two design works of Reversible D-Latch

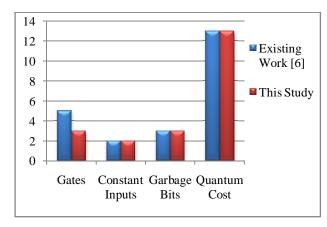

|               | No. Of gates | No. of   | No. of  | Quantum |

|---------------|--------------|----------|---------|---------|

|               |              | Constant | Garbage | Cost    |

|               |              | Inputs   | Bits    |         |

| Existing Work | 5            | 2        | 3       | 13      |

| [6]           |              |          |         |         |

| This Study    | 3            | 2        | 3       | 13      |

Table 3: Comparative Experimental Results of Different Reversible T-FlipFlop

Figure 11: Graphical representation of comparison of two design works of Reversible T-FlipFlop

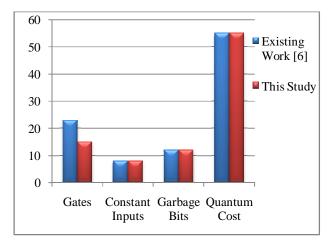

|               | No. Of gates | No. of   | No. of  | Quantum |

|---------------|--------------|----------|---------|---------|

|               |              | Constant | Garbage | Cost    |

|               |              | Inputs   | Bits    |         |

| Existing Work | 23           | 8        | 12      | 55      |

| [6]           |              |          |         |         |

| This Study    | 15           | 8        | 12      | 55      |

Table 4: Comparative Experimental Results Of Different Reversible 4-Bit Asynchronous Up/Down Counter

Figure 12: Graphical representation of comparison of two design works of Reversible 4-Bit Asynchronous Up/Down Counter

# 6.Conclusion

This paper proposes designs of basic reversible sequential elements such as latches, flipflops and four bit reversible asynchronous up/down counter. We have shown average power dissipation in each gate in simulation part which indicates negligible energy dissipation which in turn improves performance of circuit. Basic reversible gate presented in this paper can be used in regular circuits realizing Boolean functions. The proposed asynchronous counter designs have the applications in building reversible ALU, reversible processor etc. In this paper, we present a method of asynchronous counter design directly from reversible gates. This work forms an important move in building large and complex reversible sequential circuits.

### 7.Reference

- Landauer, R., "Irreversibility and heat generation in the computing process", IBM

Research and Development, 5(3): pp. 183-191, 1961.

- 2. Bennett, C.H., "Logical reversibility of Computation", IBM J.Research and Development, 17: pp. 525-532, 1973.

- 3. R. Feynman, "Quantum mechanical computers", Optical News, vol. 11, 1985, pp. 11-20.

- 4. Abu Sadat Md. Sayem, Masashi Veda "Optimization of reversible sequential circuits" journal of computing, volume 2, issue 6, june 2010, issn 2151-9617

- Majid Haghparast and Ali Hatam "Design of a Novel Fault Tolerant Reversible Montgomery Multiplier in Nanotechnology" Australian Journal of Basic and Applied Sciences, 5(7): 234-242, 2011 ISSN 1991-8178

- 6. V.Rajmohan, V.Ranganathan,"Design of counter using reversible logic" 978-1-4244-8679-3/11/\$26.00 ©2011 IEEE

- Siva Kumar Sastry, Hari Shyam Shroff, Sk.Noor Mahammad, V. Kamakoti" Efficient Building Blocks for Reversible Sequential Circuit Design" 1-4244-0173-9106/\$20.00©2006IEEE

- 8. M.-L. Chuang and c.-Y. Wang, "Synthesis of reversible sequential elements," ACM journal of Engineering Technologies in Computing Systems (JETC), vol. 3, no. 4, 2008.

- 9. S.K.S. Hari, S. Shroff, S.N. Mohammad, and V. Kamakoti, "Efficient building blocks for reversible sequential circuit design," IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), 2006.

- 10. Thapliyal H, M. B.Sshrinivas "Novel Reversible Multiplier Architecture Using Reversible TSG Gate" Computer Systems and Applications, 2006. IEEE International Conference on.

- 11. Rangaraju H G, Venugopal V, Muralidhara K N, Raja K B "Low Power Reversible Parallel Binary Adder/Subtractor" International journal of VLSI design & Communication Systems (VLSICS) Vol 1, No.3, September 2010

- 12. H.R.Bhagyalakshmi, M.K.Venkatesha" An improved design of multiplier using reversible logic gates" International Journal of Engineering Science and Technology Vol. 2(8), 2010, 3838-3845

- 14. Thapliyal H, Ranganathan N.," Design of Reversible Latches Optimized for Quantum Cost, Delay and Garbage Outputs" Centre for VLSI and Embedded System Technologies International Institute of Information Technology, Hyderabad, 500019, India

- 15. Haghparast, M., M. Mohammad, K. Navi and M. Eshghi, 2009. Optimized reversible multiplier circuit. J. Circuits Syst. Comp., 18(2): 311-323.

- 16. Mozammel H A Khan and Marek Perkowski" Synthesis of Reversible Synchronous Counters" 2011 41st IEEE International Symposium on Multiple-Valued Logic

- 17. Thapliyal and A.P. Vinod, "Design of reversible sequential elements with feasibility of transistor implementation," International Symposium on Circuits and Systems (ISCAS 2007), 2007, pp. 625-628.